Исследование основных логических элементов и комбинационных устройств. Исследование логических элементов и синтез логических схем Краткие теоретические сведения

Цель работы . Ознакомление с основными функциями и законами алгебры логики, характеристиками логических микросхем, основами анализа и синтеза простых и сложных логических схем.

Краткие теоретические сведения.

Анализ работы цифровых устройств и синтез логических цепей производится на основе математического аппарата алгебры логики или «булевой» алгебры, оперирующей только двумя понятиями: истинным (логическая «1») и ложным (логический «0»). Функции, отображающие такую информацию, а также устройства, формирующие функции алгебры логики, называются логическими. Логические функции нескольких переменных определяют характер логических операций, в результате которых набору входных переменных x 0 , x 1 ,…, x n -1 ставится в соответствие выходная переменная F

F = f (x 0 , x 1 ,…, x n -1 ).

Функция преобразования характеризуется таблицей, в которой каждой комбинации входных переменных соответствует значение выходной переменной F . Ее называют таблицей истинности.

Основными функциями алгебры логики, с помощью которых можно осуществлять любые логические преобразования, являются логическое умножение (конъюнкция), логическое сложение (дизъюнкция) и логическое отрицание (инверсия).

Алгебра логики позволяет преобразовывать формулы, описывающие сложные логические зависимости, с целью их упрощения. Это помогает в конечном итоге определять оптимальную структуру того или иного цифрового автомата, реализующего любую сложную функцию. Под оптимальной структурой принято понимать такое построение автомата, при котором число входящих в его состав элементов минимально.

Основные законы алгебры логики .

Переместительный закон:

a + b = b + а; ab = ba .

Сочетательный закон:

(a + b) + c = a + (b + c); (ab)c = a(bc).

Распределительный закон:

a(b + c) = ab + ac; a + bc = (a + b)(a +c).

Закон поглощения:

a + ab = a(1 + b) = a; a(a + b) = a + ab = a.

Закон склеивания:

ab

+

a

=

a

;

(a

+

b

)(a

+

)

=

a

.

)

=

a

.

Закон отрицания:

или

или

.

.

Логические элементы . Логические элементы используют в качестве значений входных и выходных напряжений лишь два уровня: «высокий» и «низкий». Если логическому «0» соответствует напряжение низкого уровня, а логической «1» – высокого, то такую логику называют положительной, и наоборот, если за логический «0» принимают напряжение высокого уровня, а за логическую «1» – напряжение низкого уровня, то такую логику называют отрицательной. В транзисторно-транзисторной логике (ТТЛ) напряжение логического «0» – U 0 составляет десятые доли вольт (менее 0,4 В), а напряжение логической «1» – U 1 >2,4 В. Логические элементы реализуют простейшие функции или систему функций алгебры логики.

|

Таблица 1 |

|

|

|

|

ростейшей

функцией алгебры логики является

функция НЕ. Она реализуется с помощью

инвертора, условное графическое

обозначение которого приведено на рис.

1. На вход инвертора подается величинаX

,

которая может принимать два значения:

«0» и «1». Выходная величина Y

,

при этом тоже принимает два значения:

«1» и «0». Взаимно однозначное соответствие

X

и Y

дается таблицей истинности (табл. 1),

причем значение выходной величины Y

зависит не от предыдущих значений, а

лишь от текущего значения входной

величины X

:

Y

=

ростейшей

функцией алгебры логики является

функция НЕ. Она реализуется с помощью

инвертора, условное графическое

обозначение которого приведено на рис.

1. На вход инвертора подается величинаX

,

которая может принимать два значения:

«0» и «1». Выходная величина Y

,

при этом тоже принимает два значения:

«1» и «0». Взаимно однозначное соответствие

X

и Y

дается таблицей истинности (табл. 1),

причем значение выходной величины Y

зависит не от предыдущих значений, а

лишь от текущего значения входной

величины X

:

Y

=

.

.Это справедливо для всех логических элементов, не имеющих памяти, у которых в таблице истинности значение Y не зависит от порядка строк.

|

Таблица 2 |

||

|

|

|

|

огическими

элементами, реализующими функции

логического сложения и логического

умножения, являются элементы ИЛИ и И.

Таблицы истинности для этих элементов

однозначно связывают значение выходной

величиныY

со значениями двух (или более) входных

величин х

l

,

х

2

,

... x

n

.

Условные графические обозначения

логических элементов ИЛИ и И приведены

соответственно на рис. 2 и 3, а их таблицы

истинности – в таблицах 2 и 3. Например,

для логического элемента 2-ИЛИ,

реализующего дизъюнкцию

огическими

элементами, реализующими функции

логического сложения и логического

умножения, являются элементы ИЛИ и И.

Таблицы истинности для этих элементов

однозначно связывают значение выходной

величиныY

со значениями двух (или более) входных

величин х

l

,

х

2

,

... x

n

.

Условные графические обозначения

логических элементов ИЛИ и И приведены

соответственно на рис. 2 и 3, а их таблицы

истинности – в таблицах 2 и 3. Например,

для логического элемента 2-ИЛИ,

реализующего дизъюнкциюY = х l + х 2 или Y = х l х 2 ,

а для элемента 2-И, реализующего конъюнкцию

Y = х l х 2 или Y = х l х 2 .

|

Таблица 3 |

||

|

|

|

|

а

наборе логических элементов И,

ИЛИ, НЕ можно реализовать любую сколь

угодно сложную логическую функцию,

поэтому данный набор элементов

называют функционально полным.

а

наборе логических элементов И,

ИЛИ, НЕ можно реализовать любую сколь

угодно сложную логическую функцию,

поэтому данный набор элементов

называют функционально полным.На практике часто используется расширенный набор логических элементов, позволяющих также составлять функционально полные системы. К ним относятся элементы:

ИЛИ-НЕ (элемент Пирса), реализующий функцию

;

;

И-НЕ (элемент Шеффера), реализующий функцию

.

.

Их обозначения и таблицы истинности приведены на рис. 4 и в табл. 4.

|

Таблица 4 |

|||

|

|

|

|

|

В частности функционально полные системы могут состоять из элементов только одного типа, например, реализующих функцию И-НЕ либо ИЛИ-НЕ.

Комбинационные логические цепи – это такие цепи, выходные сигналы которых однозначно определяются сигналами, присутствующими на их входах в рассматриваемый момент времени и не зависят от предыдущего состояния.

Набор логических элементов, входящих в состав учебного стенда по основам цифровой техники не содержит элементов, реализующих функцию ИЛИ-НЕ, что ограничивает число вариантов построения логических схем при их синтезе и позволяет составлять схемы только в базисе элементов И-НЕ.

Прежде чем перейти к вопросам анализа и синтеза логических устройств в заданном базисе элементов (И-НЕ), необходимо составить таблицу, в которую будут сведены все возможные формы представления выходных сигналов указанных элементов при условии, что на их входы поданы логические переменные х l и х 2 . При синтезе схем можно использовать два технических приема: двойное инвертирование входного исходного выражения или его части и применение теорем Де-Моргана. При этом функция преобразуется к виду, содержащему только операции логического умножения и инверсии, и переписывается через условные обозначения операции И-НЕ и НЕ.

Последовательность проведения анализа и синтеза комбинационных логических цепей:

Составление таблицы функционирования логической цепи (таблицы истинности).

Запись логической функции.

Минимизация логической функции и преобразование ее к виду, удобному для реализации в заданном базисе логических элементов (И-НЕ, НЕ).

Пример проведения анализа и синтеза логических цепей .

Пусть необходимо построить мажоритарную ячейку (ячейку голосования) на три входа, т.е. такую ячейку, у которой сигнал на выходе равен единице тогда, когда на двух или трех входах цепи присутствует сигнал единицы, в противном случае выходной сигнал должен быть равен нулю.

Вначале заполним таблицу истинности (табл. 5). Поскольку в данном случае имеются три входных сигнала х 1 , х 2 , х 3 , каждый из которых может принимать одно из двух возможных значений (0 или 1), то всего может быть восемь различных комбинаций этих сигналов. Четырем из этих комбинаций будет соответствовать выходной сигнал F , равный единице.

Таблица 5

|

x 1 |

x 2 |

x 3 | ||

Если в синтезируемой таблице истинности выходная величина чаще принимает значение «1», то синтезируются строки, в которых выходная величина равна «0».

При выполнении заданной процедуры получим функцию

F = . (1)

Для минимизации (упрощения) данной функции нужно применить основные законы алгебры логики. Возможна следующая последовательность преобразований, например, с применением закона склеивания (теоремы Де-Моргана):

F = =

+ =

= . (2)

. (2)

Как видно, полученное конечное выражение гораздо проще исходного.

Аналогично проводится анализ (составление таблиц истинности) и более сложных логических схем.

Для выполнения задания предлагается набор наиболее распространенных логических элементов (рис. 5).

Рис.

5. Набор логических элементов для

выполнения задания

Рис.

5. Набор логических элементов для

выполнения задания

Задание к лабораторной работе

1. Составить таблицы истинности для всех логических элементов, приведенных на рис. 5.

2. Для каждого логического элемента из набора представленных на рис. 5. составить логические выражения, реализующие их функции в базисе логических элементов НЕ и И-НЕ и начертить полученные тождественные схемы.

3. Собрать рассмотренные схемы на стенде и, путем перебора комбинаций входных сигналов, составить их таблицы истинности.

4. Используя законы отрицания (теоремы Де-Моргана) произвести преобразование минимизированной функции (2) для реализации ее в базисе логических элементов НЕ и И-НЕ и начертить полученную тождественную схему.

5. Собрать представленную схему на стенде и, путем перебора комбинаций входных сигналов, проверить соответствие ее работы таблице истинности (табл. 5).

Контрольные вопросы

Что такое функционально полная система и базис логических элементов?

В чем особенности синтеза логических устройств?

В чем заключаются принципы минимизации логических устройств?

Назовите основные операции булевой алгебры.

Что отражают теоремы булевой алгебры? Сформулировать теоремы Де-Моргана: поглощения и склеивания.

Какие цифровые устройства называются комбинационными?

ЛАБОРАТОРНАЯ РАБОТА № 5

Отправить свою хорошую работу в базу знаний просто. Используйте форму, расположенную ниже

Студенты, аспиранты, молодые ученые, использующие базу знаний в своей учебе и работе, будут вам очень благодарны.

HTML-версии работы пока нет.

Cкачать архив работы можно перейдя по ссылке, которая находятся ниже.

Подобные документы

Основные аксиомы и тождества алгебры логики. Аналитическая форма представления булевых функций. Элементарные функции алгебры логики. Функции алгебры логики одного аргумента и формы ее реализации. Свойства, особенности и виды логических операций.

реферат , добавлен 06.12.2010

Системы цифровой обработки информации. Понятие алгебры Буля. Обозначения логических операций: дизъюнкция, конъюнкция, инверсия, импликация, эквивалентность. Законы и тождества алгебры Буля. Логические основы ЭВМ. Преобразование структурных формул.

презентация , добавлен 11.10.2014

Булевы алгебры – решетки особого типа, применяемые при исследовании логики (как логики человеческого мышления, так и цифровой компьютерной логики), а также переключательных схем. Минимальные формы булевых многочленов. Теоремы абстрактной булевой алгебры.

курсовая работа , добавлен 12.05.2009

Свойства операций над множествами. Формулы алгебры высказываний. Функции алгебры логики. Существенные и фиктивные переменные. Проверка правильности рассуждений. Алгебра высказываний и релейно-контактные схемы. Способы задания графа. Матрицы для графов.

учебное пособие , добавлен 27.10.2013

Основы формальной логики Аристотеля. Понятия инверсии, конъюнкции и дизъюнкции. Основные законы алгебры логики. Основные законы, позволяющие производить тождественные преобразования логических выражений. Равносильные преобразования логических формул.

презентация , добавлен 23.12.2012

Основные понятия алгебры логики. Дизъюнктивные и конъюнктивные нормальные формы. Сущность теоремы Шеннона. Булевы функции двух переменных. Последовательное и параллельное соединение двух выключателей. Свойства элементарных функций алгебры логики.

контрольная работа , добавлен 29.11.2010

Понятие алгебры логики, ее сущность и особенности, основные понятия и определения, предмет и методика изучения. Законы алгебры логики и следствия из них, методы построения формул по заданной таблице истинности. Формы представления булевых функций.

учебное пособие , добавлен 29.04.2009

Цель работы – Практическое изучение логических элементов, реализующих элементарные функции алгебры логики (ФАЛ ). Экспериментальное исследование логических элементов, построенных на отечественных микросхемах серии К155, К561.

1. Краткие теоретические сведения

1.1. Математической основой цифровой электроники и вычислительной техники является алгебра логики или булева алгебра (по имени английского математика Джона Буля).

В булевой алгебре независимые переменные или аргументы (X) принимают только два значения: 0 или 1. Зависимые переменные или функции (Y) также могут принимать только одно из двух значений: 0 или 1. Функция алгебры логики (ФАЛ) представляется в виде:

Y = F (X 1 ; X 2 ; X 3 ... X N).

Данная форма задания ФАЛ называется алгебраической.

1.2. Основными логическими функциями являются:

Логическое отрицание (инверсия)

Логическое сложение (дизьюнкция)

Y = X 1 + X 2 или Y = X 1 V X 2 ;

Логическое умножение (коньюнкция)

Y = X 1 ·X 2 или Y = X 1 X 2 .

К более сложным функциям алгебры логики относятся:

Функция равнозначности (эквивалентности)

Y = X 1 ·X 2

+

или Y = X 1

~

X 2

;

или Y = X 1

~

X 2

;

Функция неравнозначности (сложение по модулю два)

Y =

+

+ или Y = X 1

X 2

;

или Y = X 1

X 2

;

Функция Пирса (логическое сложение с отрицанием)

Y =

;

;

Функция Шеффера (логическое умножение с отрицанием)

Y =

;

;

1.3. Для булевой алгебры справедливы следующие законы и правила:

Распределительный закон

X 1 (X 2 + X 3) = X 1 ·X 2 + X 1 ·X 3 ,

X 1 + X 2 ·X 3 = (X 1 + X 2) (X 1 + X 3) ;

Правило повторения

X·X = X , X + X = X ;

Правило отрицания

X· = 0 , X +

= 0 , X + = 1 ;

= 1 ;

Теорема де Моргана: Чтобы получить дополнительную булеву функцию, инвертируйте каждую переменную и замените И на ИЛИ

=

= ,

, =

= ;

;

Тождества

X·1 = X, X + 0 = X, X·0 = 0 , X + 1 = 1.

1.4. Схемы, реализующие логические функции, называются логическими элементами. Основные логические элементы имеют, как правило, один выход (Y) и несколько входов, число которых равно числу аргументов (X 1 ; X 2 ; X 3 ... X N). На электрических схемах логические элементы обозначаются в виде прямоугольников с выводами для входных (слева) и выходных (справа) переменных. Внутри прямоугольника изображается символ, указывающий функциональное назначение элемента.

На рис. 2.1 2.10 представлены логические элементы, реализующие рассмотренные ниже функции. Там же представлены так называемые таблицы состояний или таблицы истинности, описывающие соответствующие логические функции в двоичном коде в виде состояний входных и выходных переменных. Таблица истинности является также табличным способом задания ФАЛ.

На рис. 2.1 представлен элемент “НЕ.

Рисунок 2.1. Элемент “НЕ”, реализующий

функцию логического отрицания Y =

Элемент “ИЛИ” (рис. 2.2) и элемент “И” (рис. 2.3) реализуют функции логического сложения и логического умножения соответственно.

Рисунок 2.2

Рисунок 2.3

Функции Пирса и функции Шеффера реализуются с помощью элементов “ИЛИ-НЕ” и “И-НЕ”, представленных на рис. 2.4 и рис. 2.5 соответственно.

Рисунок 2.4

Рисунок 2.5

Элемент Пирса можно представить в виде последовательного соединения элемента “ИЛИ” и элемента “НЕ” (рис. 2.6), а элемент Шеффера – в виде последовательного соединения элемента “И” и элемента “НЕ” (рис. 2.7).

На рис. 2.8 и рис. 2.9 представлены элементы “Исключающее ИЛИ” и “Исключающее ИЛИ - НЕ”, реализующие функции неравнозначности и неравнозначности с отрицанием соответственно.

Рисунок 2.8

Рисунок 2.9

1.5. Логические элементы, реализующие операции коньюнкции, дизьюнкции, функции Пирса и Шеффера, могут быть, в общем случае, n - входные. Так, например, логический элемент с тремя входами, реализующий функцию Пирса, имеет вид, представленный на рис. 2.10.

Рисунок 2.10

В таблице истинности (рис. 2.10) в отличие от таблиц (рис. 2.4) имеется восемь значений выходной переменной Y. Это количество определяется числом возможных комбинаций входных переменных N, которое, в общем случае, равно: N = 2 n , где n - число входных переменных.

1.6. Логические элементы используются для построения интегральных микросхем, выполняющих различные логические и арифметические операции и имеющих различное функциональное назначение. Микросхемы типа К155ЛН1 и К155ЛА3, например, имеют в своем составе шесть инверторов и четыре элемента Шеффера соответственно (рис. 2.11), а микросхема К155ЛР1 содержит элементы разного вида (рис. 2.12).

Рисунок 2.11

Рисунок 2.12

1.7. Функции алгебры логики любой сложности можно реализовать с помощью указанных логических элементов. В качестве примера рассмотрим ФАЛ, заданную в алгебраической форме, в виде:

Упростим данную ФАЛ, используя вышеприведенные правила. Получим:

(2)

(2)

Проведенная операция носит название минимизации ФАЛ и служит для облегчения процедуры построения функциональной схемы соответствующего цифрового устройства.

Функциональная схема устройства, реализующая рассматриваемую ФАЛ, представлена на рис. 2.13.

Рисунок 2.13

Следует отметить, что полученная после преобразований функция (2) не является полностью минимизированной. Полная минимизация функции проводится студентами в процессе выполнения лабораторной работы.

Оборудование: Лабораторный стенд ЛКЭЛ – 4М 08 «Цифровая и цифро-аналоговая схемотехника»

2.1. Исследовать особенности функционирования логических элементов НЕ, 2ИЛИ, 2И, 2И-НЕ, 3И-НЕ, расположенных на панели стенда. Для исследования элемента НЕ, расположенного в левой части монтажного поля сигнал на вход подавать путем нажатия на черную кнопку. При этом свечение красного светодиода говорит о наличии «1» на входе и соответственно «0» на выходе. Для исследования остальных элементов за входной сигнал, как вариант, взять сигнал с гнезда, расположенного рядом со светодиодом. Построить таблицу истинности для каждого элемента, взяв за образец таблицу 1. Для измерений состояний и значений напряжений входа и выхода использовать осциллограф (вольтметром, расположенным на стенде).

2.1.1. Минимизировать функцию (2) используя различные варианты (можно один), разработать схему, исходя из наличия элементов на панели стенда, и реализовать ее на панели стенда. Результаты занести в таблицу 2.

2.1.2. По результатам исследований (п. 2.1.1) определить функциональное назначение элементов и проставить их обозначение на схеме в лабораторном отчете.

Название и цель работы.

Схема выполнения экспериментов.

Заполненные таблицы 2.1 и 2.2.

Результаты измерений U 0 и U 1 (п. 2.1).

Выводы по работе.

4. Контрольные вопросы.

Какими значениями переменных оперирует алгебра логики?

Основные формы задания ФАЛ.

Вид основных логических функций в алгебраической форме.

Что такое “логический элемент”?

Какие логические функции выполняют элементы Пирса и Шеффера?

Чем определяется число возможных комбинаций входных переменных для произвольного логического элемента?

Дать определение СДНФ, СКНФ.

Таблица 2.1 Таблица 2.2

Лабораторная работа №2

Литература:

2. В.С. Ямпольский Основы автоматики и ЭВТ. – М.: Просвещение. - 1991. - §3.1 ‑3.4

Ход работы:

- Включить терминал, подключиться к локальной сети и загрузить сайт «Основы микроэлектроники». Выбрать номер лабораторной работы, зарегистрироваться и приступить к выполнению заданий согласно появляющимся на экране инструкциям и данному описанию.

- В каждом из 10 заданий выделить из приведенной схемы цифрового автомата узел, содержащий только логические элементы, и изобразить его принципиальную схему, используя УГО российского стандарта

- Смоделировать работу каждой схемы средствами Electronic Workbench и составить таблицу истинности исследуемого устройства

- Определить логическую функцию исследуемого устройства и привести его условное графическое изображение (УГО)

- В каждом задании составить дополнительно две схемы реализации той же логической функции на элементах 2И-НЕ (элемент Шеффера) и элементах 2ИЛИ-НЕ (элемент Пирса), используя минимальное количество вентилей

- В задании 11 по аналогии с предыдущими схемами дополнить приведенное устройство схемой узла, позволяющего подавать на входы Х1¸Х3 произвольную комбинацию логических сигналов и индицировать состояние каждого входа и выхода. Исследовать работу схемы аналогично предыдущим заданиям

Отчет к каждому заданию лабораторной работы оформлять по образцу, приведенному в ПРИЛОЖЕНИИ 1.

При защите работы уметь объяснить каждый из полученных результатов.

ПРИЛОЖЕНИЕ 1

Фрагмент отчета (на примере одного задания)

Задание 1.

Пример схемы, приведенной в задании.

В таком виде перерисовывать её не нужно !

Фрагмент отчета по данному заданию приводится ниже.

Задание 1: выполняемая схемой функция ‑ «2И-НЕ»

Схема: УГО: Таблица истинности:

«2И-НЕ» на элементах Шеффера. «2И-НЕ» на элементах Пирса.

ПРИЛОЖЕНИЕ 2

УГО и таблицы истинности некоторых логических элементов

1. Элемент «2И-НЕ»

2. Элемент «2ИЛИ-НЕ»

3. Элемент «исключающее ИЛИ»

ПРИЛОЖЕНИЕ 3

Примеры условных графических обозначений логических элементов по ГОСТ (российский стандарт) и ANSI (American National Standard Institute)

| УГО по ANSI | УГО по ГОСТ | Функциональное назначение |

| «2И» (2-Input AND Gate) | ||

| «3И» (3-Input AND Gate) | ||

| «2И-НЕ» (2-Input NAND Gate) | ||

| «2ИЛИ» (2-Input OR Gate) | ||

| «2ИЛИ-НЕ» (2-Input NOR Gate) | ||

| «3ИЛИ-НЕ» (3-Input NOR Gate) | ||

| «НЕ» (NOT Gate) | ||

| «исключающее ИЛИ» (2-Input XOR Gate) | |

| «исключающее ИЛИ-НЕ» (2-Input XNOR Gate) | ||

| 6-входовый сумматор по модулю 2 (6-Input XOR Gate) |

Лабораторная работа № 3.

Исследование триггеров RS-, RST-, D- и JK-типов.

Литература:

1. А.А. Коваленко, М.Д. Петропавловский. Основы микроэлектроники: Учебное пособие. ‑ Барнаул: Изд‑во БГПУ, 2005. – 222 с.

2. В.С. Ямпольский. Основы автоматики и электронно-вычислительной техники. – М.: Просвещение. – 1991. – 223 с.

4. Руководство к выполнению виртуальных лабораторных работ с помощью программы моделирования электрических схем Electronic Workbench 5.12

Ход работы:

- Включить терминал, подключиться к локальной сети и загрузить сайт «Основы микроэлектроники». Выбрать номер лабораторной работы, зарегистрироваться и приступить к выполнению заданий согласно появляющимся на экране инструкциям и данному описанию

- Исследуйте работу асинхронного RS-триггера с инверсными входами на логических элементах 2И-НЕ.

Пользуясь программой Electronics Workbench, соберите схему триггера, приведенную на рисунке.

Для управления триггером используйте переключатели (Switch), подсоединяющие входы к клемме плюса питания (V cc) либо к клемме земли (Ground), а для индикации состояния входов и выходов – пробники (соответственно Green Probe и Red Probe).

Исследование провести в следующем порядке:

Таблица состояний триггера

| № комбинации | Операция | ||

| Установка выхода | |||

В сокращенном варианте таблицу состояний RS-триггера с инверсными входами принято изображать в следующем виде (при данной комбинации входных сигналов выход Q устанавливается в указанное состояние независимо от его предыдущего состояния):

Здесьсимвол (t+1) означает состояние триггера «в следующем такте», т.е. после установления выхода в соответствии со входными сигналами

Здесьсимвол (t+1) означает состояние триггера «в следующем такте», т.е. после установления выхода в соответствии со входными сигналами

Примечание: (в этой и других подобных таблицах приняты следующие обозначения ):

- Исследуйте работу асинхронного RS-триггера с прямыми входами на логических элементах 2И-НЕ.

Для этого добавьте к собранной схеме еще 2 элемента 2И-НЕ, чтобы получить триггер с прямыми входами (см. рисунок), и на основе эксперимента в среде Electronics Workbench по аналогии с предыдущим заданием заполните таблицу его состояний

Для этого добавьте к собранной схеме еще 2 элемента 2И-НЕ, чтобы получить триггер с прямыми входами (см. рисунок), и на основе эксперимента в среде Electronics Workbench по аналогии с предыдущим заданием заполните таблицу его состояний

- Исследуйте работу синхронизируемого RS-триггера (RST-триггера).

|

Для этого откройте схему RST-триггера (файл E:\MeLabs\Lab3\rst_trig_analis.EWB), ко входам которого подключен генератор слова (Word Generator), а все входные и выходные сигналы контролируются логическим анализатором (Logic Analyzer). Разверните панель генератора слова и установите для него режим пошаговой работы (Step). Введите в память генератора 16-ричные коды слов Вашего варианта. Разверните панель логического анализатора. Включите моделирование и, последовательно нажимая ЛКМ на находящуюся на панели генератора слова клавишу «Step», сгенерируйте всю тестовую последовательность. Зарисуйте в тетрадь полученные логическим анализатором диаграммы. Заполните потактовую таблицу состояний триггера.

Таблица состояний триггера

| Информац. сигнал | Номера тактов | |||||||||

| C | ||||||||||

| R | ||||||||||

| S | ||||||||||

| Q |

- Исследуйте работу статического и динамического D‑триггеров. Откройте схему параллельно включенных статического и динамического D‑триггеров (файл E:\MeLabs\Lab3\D_trig.EWB), ко входам которых подключен генератор слова (Word Generator), а все входные и выходные сигналы контролируются пробниками.

|

Разверните панель генератора слова. Из таблицы состояний выпишите по тактам двоичные коды слов и, преобразовав их в 16-ные, введите в память генератора слов. Включите моделирование и, последовательно нажимая ЛКМ на находящуюся на панели генератора слова клавишу «Step», сгенерируйте всю тестовую последовательность. Заполните потактовую таблицу состояний триггеров.

Таблица состояний триггеров

| Информац. сигнал | Номера тактов | |||||||||

| C | ||||||||||

| D | ||||||||||

| Q стат. | ||||||||||

| Q дин. |

- Откройте схему JK-триггера с динамическим управлением (jk_триг_анализ).

|

Разверните панель генератора слова и установите для него режим пошаговой работы (Step). Введите в память генератора 16-ричные коды слов Вашего варианта. Включите моделирование и, последовательно нажимая ЛКМ на находящуюся на панели генератора слова клавишу «Step», сгенерируйте всю тестовую последовательность. Зарисуйте в тетрадь полученные логическим анализатором диаграммы. Заполните потактовую таблицу состояний триггера.

Таблица состояний триггера

| Информац. сигнал | Номера тактов | |||||||||||

| C | ||||||||||||

| J | ||||||||||||

| K | ||||||||||||

| Pre | ||||||||||||

| Clr | ||||||||||||

| Q |

Замечание: В отличие от ранее исследовавшихся схем в этом задании исследуется работа конкретной микросхемы 7476 (Dual JK MS‑SLV FF (pre, clr)), в связи с чем при моделировании необходимо к соответствующим выводам подключить источник питания Vcc и заземление GND. В задании задействованы выводы только одного из JK-триггеров (первого). Входы Pre (предустановка) и Clr (очистка) играют роль установочных входов S и R соответственно.

- Выберите из библиотеки Digital интегральную схему JK-триггера 7472 (And‑gated JK MS‑SLV FF (pre, clr)) и соберите на ней схему счетного триггера. Обратите внимание, что на информационных входах используется логика 3И. Вывод NC микросхемы – свободный (не используется).

Подайте на вход триггера однополярные амплитудой 5 В прямоугольные импульсы от функционального генератора требуемой частоты, получите осциллограммы входного и выходного сигналов. Продемонстрируйте их преподавателю.

Подайте на вход триггера однополярные амплитудой 5 В прямоугольные импульсы от функционального генератора требуемой частоты, получите осциллограммы входного и выходного сигналов. Продемонстрируйте их преподавателю.

Лабораторная работа №2

1. ЦЕЛЬ РАБОТЫ

Исследование функционирования типовых логических элементов; реализация основных и других функций на базовых элементах И-НЕ и ИЛИ-НЕ; применение логических элементов как коммутаторов сигналов.

2. ТЕОРЕТИЧЕСКИЕ ПОЛОЖЕНИЯ

Микросхемы типа ЛАвыполняют логическую функцию mИ - НЕ, ИС типа ЛЕ выполняют логическую функцию mИЛИ - НЕ (m - число входов), а ИС типа ЛН выполняют логическую функцию НЕ. В одном корпусе микросхемы ЛАЗ содержится четыре логических элемента 2И-НЕ. В одном корпусе микросхемы ЛЕ1 содержится четыре логических элемента 2ИЛИ-НЕ. В одном корпусе микросхемы ЛН1 содержится шесть логических элементов НЕ (инверторов). Микросхема ЛН1 имеет двухтактный выходной каскад. Условные обозначения и цоколевки микросхем ЛАЗ, ЛЕ1 и ЛН1 приведены на рис. 1.

Рисунок 1

Логические элементы называют еще вентилями (коммутаторами сигналов). Это объясняется тем, что они могут задерживать или пропускать цифровую информацию по принципу обычного вентиля, предназначенного для управления потоком жидкости. Условное обозначение вентиля 2И с сигналами на его входах и выходе и временные диаграммы его работы в качестве коммутатора приведены на рис. 2.

Рисунок 2

Если на верхний вход логического элемента 2И подать прямоугольные импульсы с генератора, а на нижний вход - уровень логической единицы, то импульсы с генератора будут проходить на выход логического элемента 2И (рис. 2). Это следует из закона функционирования элемента И. Если же логическую единицу на нижнем входе заменить логическим нулем, то импульсы с верхнего входа на выход логического элемента 2И проходить не будут, так как хотя бы один нуль на входе этого элемента дает нуль на выходе.

3. ОБОРУДОВАНИЕ

В качестве измерительной аппаратуры используются стенд ЦС-02.

4. ПОРЯДОК ВЫПОЛНЕНИЯ РАБОТЫ

В работе используйте микросхемы K155JIA3, К155ЛЕ1, К155ЛН1.

1. Исследование функционирования логических элементов 2И-НЕ, 2ИЛИ-НЕ и НЕ

1.1. Зарисуйте схемы для исследования логических элементов (см. рис. 3 а - в). Проставьте на них номера выводов выбранных элементов микросхем. Выберите источники ЛУ, которые Вы будете использовать, и проставьте их номера на схеме.

1.2. Соберите поочередно схемы, показанные на этих рисунках.

1.3. Изменяя комбинации входных сигналов, контролируйте состояние выхода исследуемого логического элемента светодиодным индикатором или осциллографом. Заполните таблицы истинности элементов (табл. 1).

Таблица 1

| А | В | ЛА3 | ЛЕ1 | ЛН1 |

| Функция |

1.4. Убедитесь в правильности функционирования логических элементов.

Рисунок 3

2. Реализация основных функций на базовых элементах И-НЕ

2.1. Зарисуйте схемы, показанные на рис. 4,а, 4,в. Проставьте на них номера выводов выбранных элементов микросхем. Выберите источники ЛУ, которые Вы будете использовать, и проставьте их номера на схеме.

Рисунок 4

Рисунок 4

2.2.Соберите поочередно схемы, показанные на этих рисунках.

2.3.Изменяя комбинации входных сигналов, контролируйте состояние выходов всех логических элементов схем светодиодными индикаторами или осциллографом. Составьте таблицы истинности исследуемых схем.

2.4.Убедитесь в правильности полученных результатов, теоретически проанализировав работу исследуемых схем.

2.5.Используя полученные таблицы истинности, определите вид функции, которую выполняет каждая схема и запишите название функции в графу «вид функции» таблиц.

3. Реализация основных функций на базовых элементах ИЛИ-НЕ

3.1. Зарисуйте схемы, показанные на рис.5, а, б, в. Проставьте на них номера выводов выбранных элементов микросхем. Выберите источники ЛУ, которые Вы будете использовать и проставьте их номера на схеме.

Рисунок 5.

Рисунок 5.

3.2. Соберите поочередно схемы, показанные на этих рисунках.

3.3. Изменяя комбинации входных сигналов, контролируйте состояние выходов всех логических элементов схем светодиодными индикаторами или осциллографом. Заполните таблицы истинности исследуемых схем, аналогичные табл. 3...5.

3.4. Убедитесь в правильности полученных результатов, теоретически проанализировав работу исследуемых схем.

3.5. Используя таблицы истинности, определите вид функции, которую выполняет каждая схема, и запишите название функции в графу «вид функции» таблиц.

4. Реализация функций различных типов на базовых элементах И-НЕ и ИЛИ-НЕ

4.1. Зарисуйте схемы, показанные на рис.6, а, б. Проставьте на них номера выводов выбранных элементов микросхем. Выберите источники ЛУ, которые Вы будете использовать, и проставьте их номера на схеме.

Рисунок 6

4.2. Соберите поочередно схемы, показанные на этих рисунках.

4.3. Изменяя комбинации входных сигналов, контролируйте состояние выходов всех логических элементов схем светодиодными индикаторами или осциллографом. Заполните таблицы истинности исследуемых схем.

4.4. Убедитесь в правильности полученных результатов, теоретически проанализировав работу исследуемых схем.

5. Применение логических элементов в качестве коммутаторов сигналов

5.1. Зарисуйте схемы для исследования логических элементов (см. рис.7, а - г). Проставьте на них номера выводов выбранных для исследования логических элементов микросхем. Выберите источники ЛУ, которые Вы будете использовать и проставьте их номера на схеме.

5.2. Соберите поочередно схемы, показанные на рис.7, а, в, если для контроля входных и выходных сигналов имеются только светодиодные индикаторы. При наличии осциллографа соберите схемы, показанные на рис.7, в, г.

5.3. Наблюдайте форму сигнала на входе А логических элементов и выходного сигнала С сначала при наличии логической единицы на входе В, а затем - при наличии логического нуля. Для этого подключите к выходу схем (рис.7, а, в) светодиодный индикатор. При исследовании схем (рис.7, в, г) вход первого канала осциллографа подключите ко входу А логического элемента, а вход второго канала - к выходу логического элемента. Синхронизируйте развертку осциллографа сигналом первого канала. Зарисуйте временные диаграммы (осциллограммы) сигналов на входах и выходе исследуемых элементов для обоих случаев (рис. 8 а, б).

5.4. Убедитесь в правильности функционирования логических элементов, как коммутаторов сигналов, теоретически проанализировав их работу.

Рисунок 7

Рисунок 8

Отчет по работе должен содержать:

Наименование работы и цель работы;

Исследуемые схемы;

Таблицы истинности;

Временные диаграммы;

Сравнение экспериментальных данных с результатами теоретического анализа;

Выводы по работе.

КОНТРОЛЬНЫЕ ВОПРОСЫ

1. Сколько различных комбинаций существует для четырех входных сигналов?

2. Как выглядит условное обозначение логического элемента ЗИЛИ?

3. Как изменится выходная функция логического элемента И-НЕ, если его входы проинвертировать?

4. Какие логические элементы инвертируют входные сигналы, когда пропускают их на выход?

5. Какие сигналы надо подать на два остальных входа логического элемента ЗИЛИ, чтобы импульсы с первого входа проходили на выход?

Последние материалы сайта

Видео

Как создать pdf файл Создать новый файл pdf

В этой статье Вы узнаете, как сделать ПДФ файл самым простым способом и без всяких платных программ. Но сделать PDF файл – это только пол дела, ведь главное знать, как это все потом применить, а главное, как на этом заработать. Читайте статью до конца, и

Windows 8

Конвертирование файлов ODT в DOC онлайн Конвертировать презентацию openoffice в word онлайн

Многие пользователи сталкиваются с файлами, имеющими разрешение odt, и тут же возникает проблема с их открытием. В этой статье выясним, какие данные могут содержаться в файлах формата odt и какие программы смогут их отобразить. ODT – это аббревиатура от

Windows 8

Важная информация про ютуб плейлисты Что такое плейлист в youtube

06 Сен 2016 В этой статье поговорим про плейлисты на YouTube, а именно: как добавить плейлист на youtube, как создать плейлист на youtube, как правильно настроить плейлист на youtube, как добавить youtube плейлист на сайт, как добавить плейлист в разделы

Браузеры

Что делать, если Play Market пишет «Ожидание сети Wi-Fi

Процесс скачивания программ, книг и игр становится намного проще, если воспользоваться возможностями магазина Плей Маркет, который доступен для пользователей смартфонов, работающих на системе Андроид. Для открытия ресурса требуется интернет. Наиболее про

Социальные сети

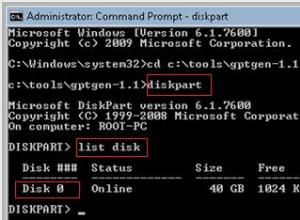

Выбранный диск имеют стиль разделов GPT

Сегодня мы разберемся, как установить любую современную версию Windows (в том числе Windows 7 или Windows 10) на жесткий диск, с таблицей разделов GPT на устаревшем компьютере с BIOS, который не поддерживает современную . Необходимость выполнить такой трю

Windows 8

Что делать, если появилась неопознанная сеть

Возникает она, как правило, при смене домашнего модема либо переезде на новое место жительства. Как часто говорят в таких случаях, что вроде все работало и ничего не меняли. Но тем не менее здесь есть некоторые нюансы. Значит так, друзья, давайте сразу пр